PIPE SerDes Architecture for PCIe Gen 5 and Beyond - Verification - Cadence Blogs - Cadence Community

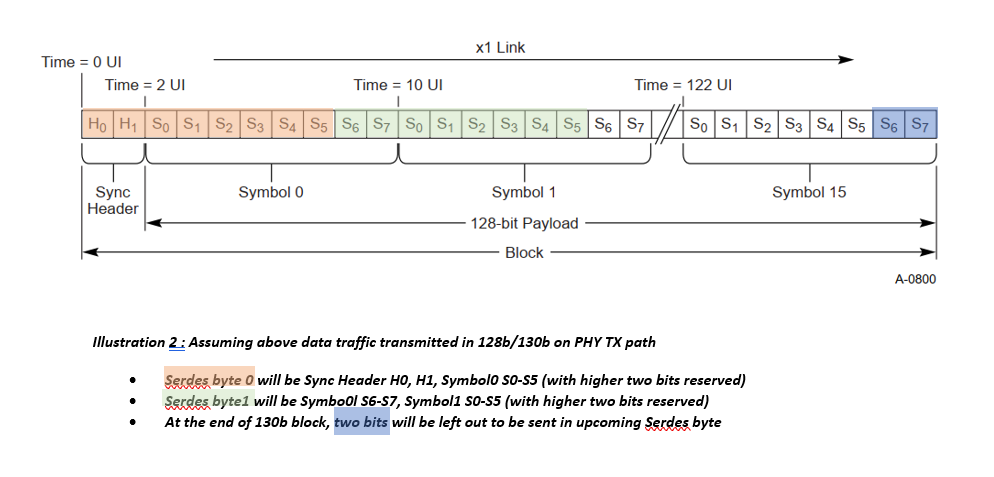

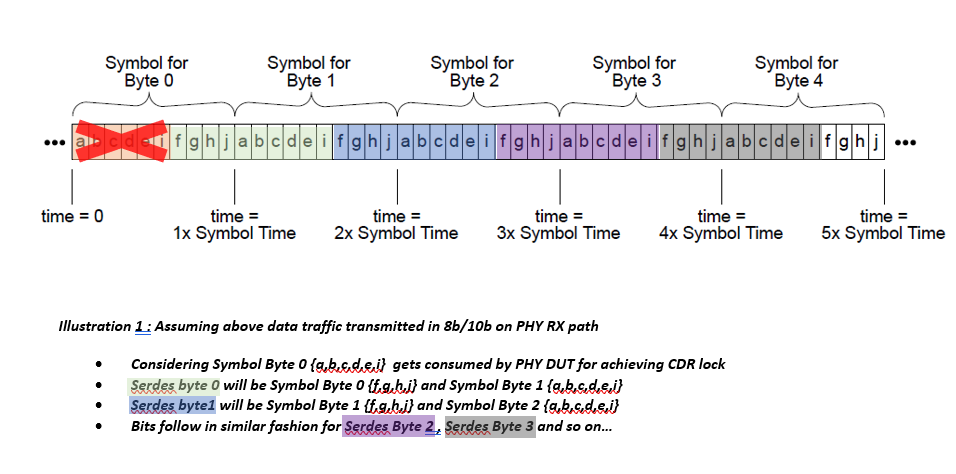

Demystifying PIPE interface packets using the in-built descrambler module in UltraScale+ Devices Integrated Block for PCI Express Gen3

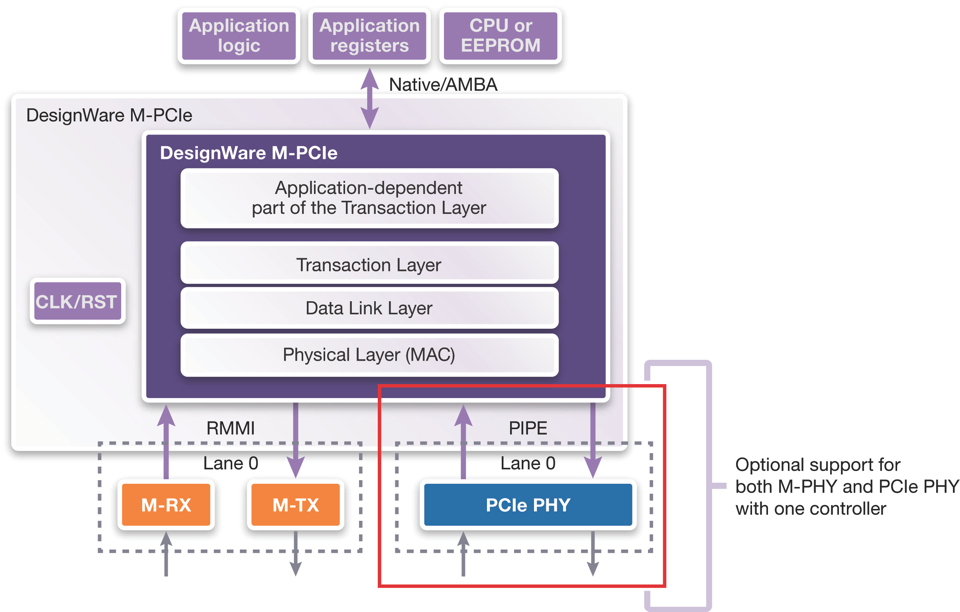

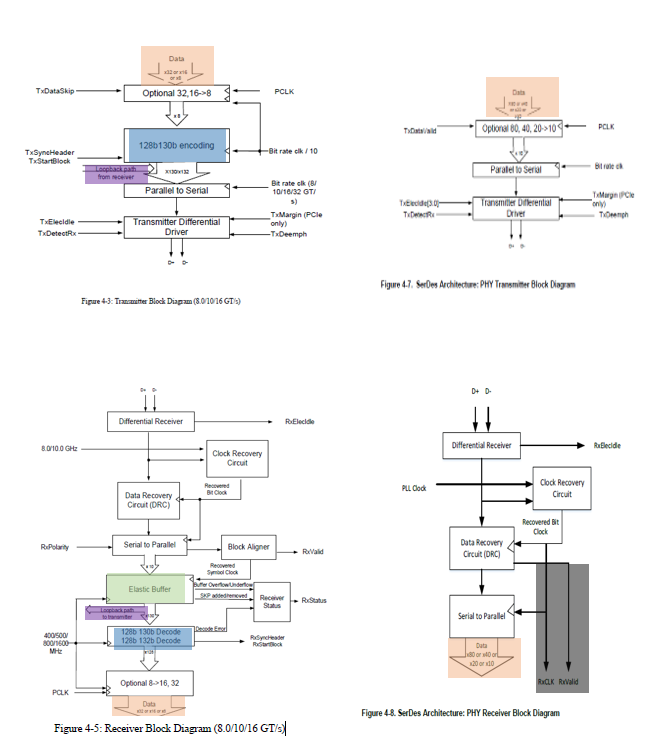

PIPE SerDes Architecture for PCIe Gen 5 and Beyond - Verification - Cadence Blogs - Cadence Community

PIPE SerDes Architecture for PCIe Gen 5 and Beyond - Verification - Cadence Blogs - Cadence Community